Intels CEO Pat Gelsinger und Dr. Ann Kelleher geben am 26. Juli um 23 Uhr im Zuge des virtuellen Intel Accelerated Webcasts (zur Übertragung) einen tieferen Einblick in die Fertigungs- und Packaging-Roadmap des Herstellers bis 2025 und stellen neue Fertigungstechnologien vor. Die ehrgeizigen Pläne umfassen einen jährlichen Fertigungsfortschritt mit Leistungs-pro-Watt-Gewinnen im zehn bis 20 Prozentbereich, ehe 2024 die sogenannte Ångström-Ära eingeleitet werden soll, die viele Neuerungen mit sich bringen wird. Außerdem stellt Intel mit RibbonFET eine neue Transistor-Architektur und mit PowerVia ein Verfahren zur Stromversorgung eines Chips von der Unterseite aus vor.

Intels IDM 2.0 Strategie

Intel hat bereits am 23. März die IDM 2.0 Strategie (zum Beitrag) vorgestellt. Diese Abkürzung steht für integrated device manufacturer und bedeutet, dass Intel Chips nicht nur selbst designt, sondern eben auch fertigt und die Software dafür programmiert – das ist weltweit einzigartig. So lässt Konkurrent AMD seine Chips zum Beispiel vom Auftragsfertiger TSMC produzieren. In allen drei Bereichen – insbesondere der Fertigung – will Intel in den nächsten Jahren mächtig aufrüsten. So holte Intel unter CEO Pat Gelsinger nicht nur viele ehemalige Chefentwickler wieder zurück ins Boot, sondern will auch Milliarden in eine neuen Chipfabrik in Europa investieren (zum Artikel von Spiegel) . Das Ziel ist dabei klar definiert, man will in allen Segmenten die Marktführung zurückerobern beziehungsweise ausbauen.

©Intel

Neues Naming für den Fertigungsprozess

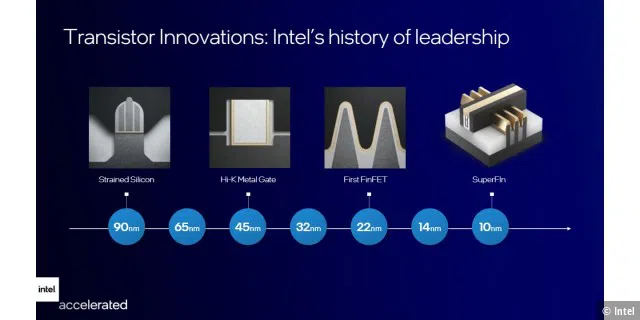

Es folgt ein kurzer Rückblick über die Fertigungsverfahren und die technologischen Fortschritte der vergangen Jahre begonnen mit dem 90-nm-Verfahren, das erstmals bei der Pentium 4 Extreme Edition zusammen mit dem strained silcion Verfahren zum Einsatz kam. Die Zeitreise setzt sich bis zum aktuellen 10-nm-SuperFin-Verfahren fort. Intel merkt dabei jedoch an, dass die angegebene Größe des Fertigungsverfahren – gemäß der ursprünglichen Definition – schon seit 1997 nicht mehr wirklich stimmt.

©Intel

Exkurs: Fertigungsdichte und Gate-Länge

Die Leistungsfähigkeit eines Prozessors bestimmt sich vor allem durch seine Fertigungsdichte, welche in erster Linie durch das Fertigungsverfahren und die Chip-Größe festgelegt wird. Die Strukturgröße gibt dabei die kleinstmögliche Kantenlänge der Plotter-Einheit zur Erzeugung der Strukturen mittels Unterbelichtung oder Diffusion an. Bei dieser kleinsten Struktur handelte es sich Anfangs um die Gate-Länge. Oder anders gesagt, wenn das Gate eine Länge von 300 Nanometern hatte, dann kam ein 300-nm-Fertigungsprozess zum Einsatz.

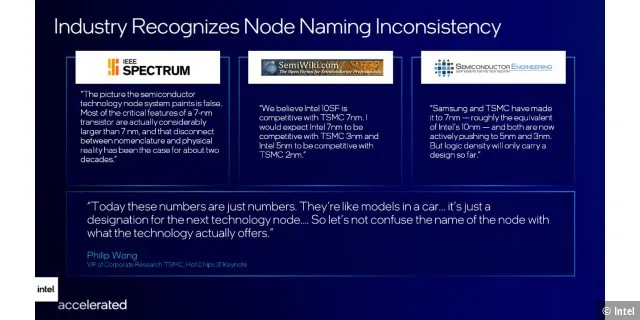

An diese ursprüngliche Definition halten sich die Chip-Hersteller allerdings seit über 20 Jahren schon nicht mehr. Das hat zur Folge, dass Intels 10-nm-Prozess auf eine ähnliche Fertigungsdichte kommt wie TSMCs 7-nm-Fertigungsverfahren, obwohl die Zahlen etwas anderes suggerieren.

Philip Wong, der VP of Corporate Research von TSMC hat das Ganze treffend beschrieben: “Heute sind diese Zahlen nur noch eines: Zahlen. Sie sind genauso wie die Modellnummer eines Autos… es ist nur noch eine Bezeichnung für den nächsten Technologieschritt… aus diesem Grund sollte man nicht den Namen des Fertigungsverfahren mit der tatsächlichen Leistungsfähigkeit der Technologie vermischen.” Oder anders gesagt: Sie sollten die Prozessoren unterschiedlicher Hersteller nicht an Hand der Zahl in ihrem jeweiligen Fertigungsverfahren vergleichen. So zeigt auch unser CPU-Vergleich (zum Beitrag) , dass Intel trotz nominell doppelt so großem Fertigungsverfahren – 14 Nanometer vs 7 Nanometer – noch ganz gut mit den Konkurrenzprodukten von AMD mithalten kann.

©Intel

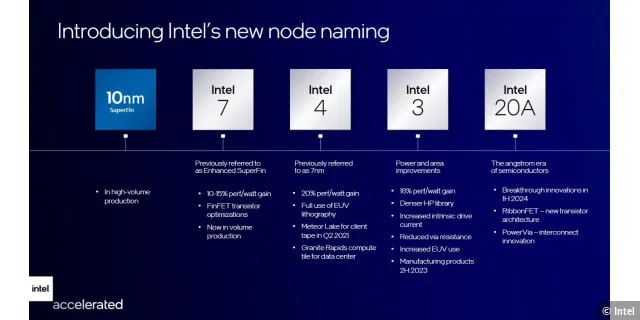

Mit diesen irreführenden Bezeichnungen soll bei Intel jetzt jedoch Schluss sein. Stattdessen führt der Hersteller ein neues Naming ein. So folgt nach dem aktuellen 10nm-SuperFin-Verfahren die sogenannte Intel 7 Node. Ursprünglich bezeichnete der Hersteller diesen Fertigungsschritt als EnhancedSuperFin-Verfahren. Dieses soll unter anderem für Alder Lake und Sapphire Rapids zum Einsatz kommen und soll durch eine Optimierung der FinFET Transistoren einen Performance-Gewinn von zehn bis 15 Prozent pro Watt ermöglichen. Über diese Prozesse und die daraus entstehden Prozessor-Architekturen haben wir bereits im Zuge des Intel Architecture Day 2020 (zum Beitrag) berichtet.

©Intel

Es folgt die Intel 4 Node, welche das ursprüngliche 7-nm-Verfahren namentlich ersetzen soll. Hierbei will der Hersteller auf eine ganzflächige EUV-Lithografie setzen. Die extrem ultraviolette Strahlung soll eine Strukturverkleinerung und damit einhergehend eine effizientere, schnellere und günstigere Belichtung der Waver zur Chip-Herstellung ermöglichen. Hierdurch verspricht Intel sich 20 Prozent mehr Performance-pro-Watt. Dieses Fertigungsverfahren soll für Meteor Lake zum Einsatz kommen. Auch Granite Rapid setzt auf Intel 4 und soll – wie auch die aktuellen Ryzen und Threadripper Prozessoren von AMD – auf einen Ansatz mit mehreren Chiplets setzen. Intel verspricht sich dadurch nicht nur eine leichtere Fertigung, sondern will mit EMIB auch einen Weg zur Kommunikation zwischen den Dies gefunden haben, um nahezu die Leistung eines monolithischen Chips zu erreichen. Die Produktion soll in der zweiten Hälfte 2022 starten und die Produkte dann Anfang 2023 an den Markt gehen.

Mit Intel 3 will der Hersteller die Leistung pro Watt erneut um 18 Prozent steigern. Ermöglichen sollen das Optimierungen des FinFET-Verfahrens sowie ein stärkerer Einsatz der EUV-Lithografie. Die Produktion soll in der zweiten Hälfte 2023 starten, mit den ersten Produkten ist dementsprechend Anfang 2024 zu rechnen.

©Intel

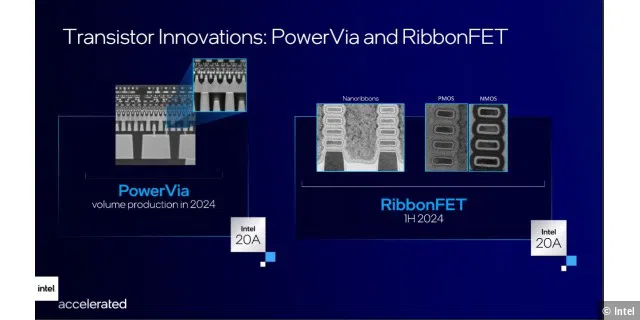

Intel 20A soll dann die sogenannte Ångström-Ära einläuten. Ein Ångström ist eine nach dem schwedischen Physiker Anders Jonas Ångström benannte Längeneinheit und entspricht dem zehnmillionsten Teil eines Millimeters. Das entspricht der einer Länge von 10 -10 Metern, ein Nanometer sind dagegen 10 -9 Meter. Im gleichen Zug will Intel die neue RibbonFET- Architektur und PowerVia zur Stromversorgung von der Unterseite des Siliziums aus einführen. Der Nachfolger Intel 18A befindet sich für Anfang 2025 ebenfalls bereits in der Entwicklung und soll die RibbonFET-Architektur weiter optimieren. Hierfür arbeitet Intel an der Entwicklung der ersten High-NA-EUV-Belichtung.

EMIB und Foveros

EMIB (Embedded Multi-Die Interconnect Bridge) ist Intels 2,5D-Embedded-Bridge Lösung die bereits seit 2017 in Produkten zur Verbindung mehrerer Chiplets zum Einsatz kommt. Sapphire Rapids soll dabei das erste Intel Xeon Produkt werden, das auf EMIB setzt. Laut Intel sollen die CPUs trotz dem Chiplet Ansatz in der Lage sein, fast die gleiche Leistung wie ein monolithischer Chip zu erreichen. Setzt die aktuelle EMIB Generation noch auf einen bump pitch von 55 Mikrometern, so soll dieser Abstand mit der nächsten Generation auf 45 Mikrometer schrumpfen.

©Intel

Foveros soll die Package-Dichte deutlich steigern können durch den ersten Ansatz zum 3D-Stacking zur Verbindung mehrerer Chiplets. In Meteor Lake soll dabei die zweite Generation von Foveros zum Einsatz kommen mit einer bump pitch , also einem Abstand zwischen den Tiles von 36 Mikrometern. Der vorgesehene Leistungsbereich umfasst dabei fünf bis 125 Watt, womit die Architektur sowohl im Mobil- als auch im Desktop-Bereich zum Einsatz kommen kann.

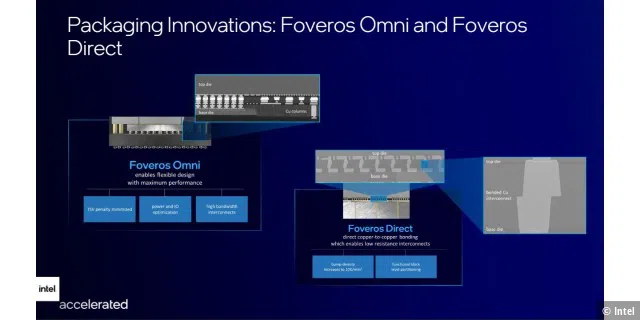

Foveros Omni ist die konsequente Weiterentwicklung mit einer optimierten 3D-Stacking-Technologie zur direkten Verbindung und Kommunikation zwischen mehreren Dies, wodurch modulare Designs ermöglicht werden. Foveros Omni soll voraussichtlich 2023 in Fertigung gehen und das Vermischen von mehreren Top-Die-Tiles mit mehreren Base-Tiles durch unterschiedliche Fab-Knoten ermöglichen.

Foveros Direct soll einen bump pitch von unter 10 Mikrometern ermöglichen und damit die Grenze zwischen dem Wafer und dem Package verschwimmen lassen. Ermöglichen sollen das direkte, niederohmige Kupfer-zu-Kupfer Verbindungen. Dadurch erhöht sich die mögliche 3D-Stacking-Dichte deutlich und ermöglicht damit neue Konzepte zum Aufbau von Rechenchips, die bisher nicht realisierbar waren. Foveros Direct wird parallel zu Foveros Omni entwickelt und soll ebenfalls 2023 verfügbar sein.